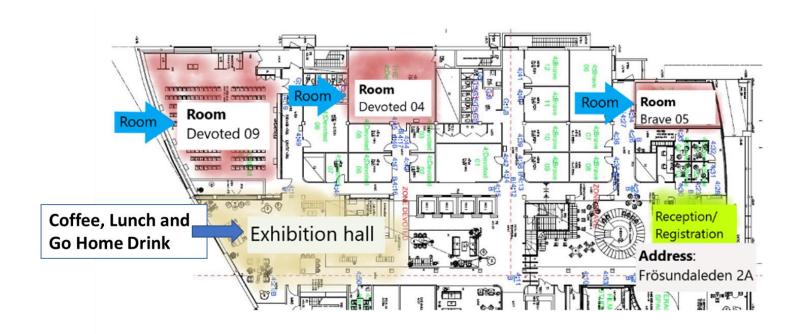

| 08:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | FPGAworld 2019<br>Registration: Stockholm, Sep 17th, Frösundaleden 2A, 169 70 Solna, SWEDEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                        |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Thank you Sponsors!    Add the least true   Mentor   SILEXICA   Me |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                        |  |  |

| 09:00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Conference Opening Björn Eriksson, ÅF and Lennart Lindh, FPGAworld Room: Devoted 09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                        |  |  |

| 09:15-10:00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Keynote Where do FPGA's outperform GPU's Keynote speaker: David Thomas, Intel PSG Room: Devoted 09  Abstract: David Thomas will talk about the big picture and market segments where FPGA based acceleration plays at its best! Is all about TCO (Total Cost of Ownership), Performance/Watt ratio's from the Edge to the Datacenter (and back). The latency, power efficiency and ability to handle various workloads will be the critical parameters defining the HW choices of our Users/customers. In addition to having an agnostic, high level SW tool. (more info) Session Chair: Lennart Lindh, FPGAworld |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                        |  |  |

| 10:00-10:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Coffee Break & Exhibition Mentor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                        |  |  |

| 10:30-12:00<br>3*30 min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Industrial/Product Track Session Chair: Lennart Lindh, FPGAworld Room: Devoted 09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Product Track Session Chair: Jesper Dahlbäck, FPGAworld Room: Devoted 04                                                                                                                             | Product Track Session Chair: Magnus Karlsson, Innowicom System Solutions AB Room: Brave 05                                                                                                                                                                             |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A: VHDL-2019 - What is important and Why Jim Lewis, SynthWorks Design Inc and chair of the IEEE VHDL Working Group, USA (more info)                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | C: Adopting Model-Based Design for FPGA, ASIC, and SoC Development Daniel Aronsson, MathWorks, USA                                                                                                   | C: Silicon Labs Clock Solutions Mike Ireland, Silicon Labs, USA                                                                                                                                                                                                        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C: Identifying & Correcting difficult to find RTL problems earlier Adam Taylor, Blue Pearl Software C: OpenVino – An introduction to Intel's OpenVino Toolkit Nikolay Rognlien, Arrow Norway AS, Norway                                                                                                                                                                                                                                                                                                                                                                                                           | C: Addressing FPGA HLS (High-level Synthesis) challenges for heterogenous computing at the edge Juan Eusse, Silexica, Germany C: Linux, Yocto and FPGAs Anders Törnqvist, Codiax, Sweden (more info) | C: Low Power AI and Machine Learning Ecosystem for products at the edge Matt Holdsworth, Lattice Semiconductor, USA (more info)  C: Vincent CDC Platform - A complete solution for Multiple Clock Domain FPGA design Reuven Dobkin, vSync Circuits, Israel (more info) |  |  |

| 12:00-13:00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Lunch Break & Exhibition and Poster Session                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                        |  |  |

| 13:00-13:30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Mike Dini talk, Dini Group, USA FPGA events during the year that has gone and gossips Session Chair: Lennart, Room: Devoted 09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                        |  |  |

| 13:30-13:45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Break & Exhibition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                        |  |  |

| 13:45-14:45<br>2*30 min                                                   | Industrial/Product Track Session Chair: Magnus Karlsson, Innowicom System Solutions AB Room: Devoted 09  A: How to accelerate the development of your embedded visions system? Andrea Leopardi, BitSim, Sweden (more info)  C: Everything you need to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Industrial Track Session Chair: Lennart Lindh, FPGAworld Room: Devoted 04  A: Getting Started with OSVVM, VHDL's #1 FPGA Verification Library Jim Lewis, SynthWorks Design Inc and chair of the IEEE VHDL Working Group, USA (more info) | Product Track Session Chair: Kim Petersen, HDC AB Room: Brave 05  C: Functional Safety for FPGAs Stefan Bauer, Mentor Booked  C: FPGA-based security solutions for IoT and Industry 4.0 Matti Tommiska, Xiphera Oy |  |  |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                           | accelerate innovation<br>Yehoshua Shoshan, Innofour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A: Introduction to FPGA VHDL<br>Verification – using the world-<br>wide exploding UVVM<br>Espen Tallaksen, Bitvis and CGI,<br>Norway (more info)                                                                                         | (more info)                                                                                                                                                                                                        |  |  |

| 14:45-15:15                                                               | Coffee Break & Exhibition SILEXICA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                    |  |  |

| 15:15-16:00                                                               | Keynote  Build and Debug Highly Reliably FPGA-based Designs Keynote speaker: Madhav Chikodikar, Director of R&D, Synopsys, Inc.  Abstract: In today's complex FPGA designs there is a need to integrate an ability to most effectively and economically deploy SEU mitigation and error monitoring circuitry in their FPGA-based systems targeting high radiation environments. In the overall design of a system, there is an opportunity to take advantage of triple modular redundancy (TMR) for creating an error detection and mitigation scheme. Important considerations include area and power increase, which affect system cost and can in some cases increase the probability of an SEU and the overall design performance challenges when applying the techniques. This presentation discusses the debug of these mitigation techniques available for different types of FPGAs. Also, the talk is about how complete some simple testing of voter logic and triplicates within the error detection and correction schemes. The combined capability of debug and fault injection allow developers to easily see each triplication and voter to verify and monitor whether the SEU mitigation techniques are working as expected. The last part is a discussion of future development to build highly reliably FPGA- based design.  Session Chair: Lennart Lindh, Room: Devoted 09 |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                    |  |  |

| 16:00-                                                                    | Go Home Drink in the Exhibition hall AGSTU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                    |  |  |

| Exhibitors<br>and Product<br>Presenters<br>Copenhagen<br>and<br>Stockholm | DTU, Technical University of Denmark ÅF, Sweden Aktuel Elektronik, Denmark Elektroniktidningen, Sweden Dini Group, USA Intel PSG, USA Mentor – A Siemens Business XILINX, USA SILEXICA, Germany PyramidTech, USA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GOWIN, China Lattice, USA Avnet Silica, Denmark Avnet Silica, Sweden Synopsys, USA BitSim, Sweden Blue Pearl Software, USA Xiphera, Finland SynthWorks, USA Bitvis and CGI, Norway VSYNC Circuits, Israel                                | Arrow, Europe Silicon Labs, Finland InnoFour, Netherlands Synective Labs, Sweden Blue Pearl Software Inc, USA MathWorks, USA Codiax, Sweden Motion Control, Sweden AGSTU FPGA Education (Yrkeshögskola), Sweden    |  |  |

# **More information**

#### Two posters:

## Boothing via CAN for GR716 microcontroller (student project)

Abstract: Presentation is base on internship at Cobham Gaisler. Cobhame Gaisler developes IP cores for fault tollerant and radiation hardened electronics used in aerospace. Technical task was to develope protocol that can be used for directly accesing memory addresses on target devices (GR716 Microcontroller) useing CAN bus. GR716 is booted with CAN routine stored on SPI memory and executes commands that are encoded from recived CAN frames from master device. Event: Stockholm

Presenter: Aleksejs Sencenko, AGSTU education

# Implementation of Measurement System Heimdall for UAV Detection (student project)

Heimdall is a system designed to develop algorithms for drone detection. The goal of Heimdall is to be able to pinpoint where a drone is in azimuth and elevation (2D) from a fixed position based on the incoming sound. Heimdall is designed to be expanded until it has a coverage of 360 degrees in azimuth angle while at the same time having enough computing power to process all the data in real time. To keep the system relatively simple to program, but still have the capacity for extended usage, the hardware used is a combination of an Arm-processor and a FPGA (Xilinx Zynq-7000).

Presenter: David Hillerström, AGSTU education

#### **Presenters:**

## VHDL-2019 - What is important and Why

**Abstract:** VHDL-2019 adds numerous features that are targeted at verification improvement. These include: interfaces, protected type improvements, an API for Assert and PSL, and conditional compilation. Interfaces allow models to handle an interface connectivity abstractly. Protected types are used to create verification data structures, such as scoreboard, coverage modeling, ... The improvements provide the next step in modeling capability. The API for Assert and PSL allows tests to get a count of errors from these sources. Jim is chair of the IEEE VHDL Working Group.

Presenter: Stockholm, Copenhagen

From: Jim Lewis, SynthWorks Design Inc, USA

# Identifying & Correcting difficult to find RTL problems earlier

**Abstract:** All engineers know the earlier we identify an issue in our design, the easier and less costly it is to correct. The worst issues are intermittent and manifest late in test or worse in the field. These late issues lead to long hours and stress in the engineering team. This session will explore common design issues which can cause these hard to find late issues, how we can address them along with outlining how they can be identified easier using Blue Pearl's Visual Verification Suite

**Presenter:** Adam Taylor, Blue Pearl Software, USA Company website: <a href="https://www.bluepearlsoftware.com/">https://www.bluepearlsoftware.com/</a>

## OpenVino - An introduction to Intel's OpenVino Toolkit

**Abstract:** Intel is investing heavily in the Computer Vision solutions with both hardware and software tools to enable customers to be efficient and competitive.

This session gives you an introduction to how Intel's distribution of "**OpenVino toolkit**" may help you convert a trained model from high level tools like TensorFlow and Caffe, to be inferenced on various hardware architectures, including FPGAs. This is applicable both for servers as well as embedded applications.

Presenter: Nikelay Pognlion, Arroy Norwey AS, Norwey

Presenter: Nikolay Rognlien, Arrow Norway AS, Norway

# Adopting Model-Based Design for FPGA, ASIC, and SoC Development

Abstract: In this presentation we talk about how to adopt Model-Based Design for chip design.

We start by defining the problem that this approach solves.

Then we describe how to adopt this approach incrementally in ways that help workflows the most.

Finally we will show results from a key customer.

Event: Stockholm

Presenter: Daniel Aronsson, MathWorks, USA

Comapany website: www.mathworks.com

# Addressing FPGA HLS (High-level Synthesis) challenges for heterogenous computing at the edge

**Abstract:** In this presentation we examine how SLX FPGA is used to take a MATLAB Embedded Coder<sup>TM</sup> generated C/C++ algorithm, in this case a Kalman filter, and optimize the C/C++ code for HLS. In this example, SLX FPGA provides more than 62x improvement in performance after auto-insertion of HLS pragmas when compared to the solution created by the HLS compiler for the original code, which had no pragmas inserted.

Event: Stockholm (Reserve Copenhagen) **Presenter**: Juan Eusse, Silexica, Germany

Comapany website: <a href="https://www.silexica.com">www.silexica.com</a>

#### Linux, Yocto and FPGAs

**Abstract:** Integrating Linux and Yocto builds into different SoCs requires many things to mange, both technical and practical. Most of this is also applicable when integrating into FPGAs containing CPU cores that can run Linux.

Event: Stockholm

Presenter: Anders Törnqvist, www.codiax.se

#### Silicon Labs Clock Solutions

**Abstract:** Silicon Labs offers the industry's broadest portfolio of crystal oscillator, clock generator, clock buffer, and jitter attenuator products and PCI Express (PCIe) clock generators and PCI Express buffers. Silicon Labs' patented technology combines best-in-class frequency flexibility with the lowest jitter in the industry, delivering quick-turn, customized solutions that simplify board design, eliminate discrete components, and maximize system performance.

Event: Stockholm

**Presenter**: Mike Ireland, www.silabs.com

#### Low Power AI and Machine Learning Ecosystem for products at the edge

**Abstract:** With faster decisions, privacy concerns and network bandwidth considerations, AI-based designers are increasingly looking to move inferencing functions out of the cloud and to the edge. Lattice small low power FPGAs and Lattice sensAI stack simplifies AI solutions for smart IoT devices. Full-featured Lattice sensAI stack includes modular hardware platforms, neural network IP cores, software tools, reference designs, and partner design services. These Flexible inferencing solutions are are optimized for <1 mW-1 W, on FPGA packages from 5.5 mm2.

Event: Stockholm

**Presenter**: Matt Holdsworth, www.latticesemi.com

## Vincent CDC Platform - A complete solution for Multiple Clock Domain FPGA design

**Abstract:** vSync Circuits Vincent CDC Platform consists of a number of EDA tools and IP libraries, enabling reliable integration and verification of multiple-clock domain designs. In addition to providing the static CDC analysis and Lint, Vincent CDC platform supports different FPGA and ASIC design flows, including simulations at RTL and gate-level. The platform identifies CDC bugs and creates auto-customized RTL solutions. The tools enable fast design CDC and Lint analyses, design reliability assessment (MTBF) and an automated bug fixing.

Presenter: Reuven Dobkin, < reuven@vsyncc.com>

Event: Stockholm

# ---- afternoon program -----

# How to accelerate the development of your embedded visions system?

**Abstract:** It is a huge task to cover everything from data collection, from for example RGB- or IR-sensors, to data analysis and, perhaps, to make decisions depending on results. BitSim has developed a platform integrating both sequential (CPU) and parallel (FPGA) processing to implement all these steps more straightforward and faster. From

embedded vision to Deep Learning, and from VHDL to Python, the entire stack is integrated into a single application making your development more agile.

Event: Stockholm, Copenhagen

Presenter: Andrea Leopardi, BitSim AB, Sweden

Comapany website: www.bitsim.com

## Everything you need to accelerate innovation

**Abstract:** Embedded software is in virtually all the products we come in contact with everyday.

As a result the use of embedded software is quickly infringing on hardware's dominance in the product development process. This presentation will cover the challenges in today's embedded software development and how we can help organizations with a unified solution that divers project transparency through real-time aggregated management information.

Event: Stockholm, Copenhagen

**Presenter**: Yehoshua Shoshan, InnoFour Comapany website: <a href="www.innofour.com">www.innofour.com</a>

## Getting Started with OSVVM, VHDL's #1 FPGA Verification Library

**Abstract:** The 2018 Wilson Research Group ASIC and FPGA Functional Verification Study revealed that Open Source VHDL Verification Methodology (OSVVM) is the #1 VHDL FPGA verification library in the world.

This getting started guide to OSVVM covers how to write transaction-based tests, message filtering, error checkers, functional coverage, constrained random tests, scoreboards, synchronization methods, and testbench utilities OSVVM's simple, readable, and powerful methodology provides a complete solution for FPGA or ASIC verification.

Event: Stockholm, Copenhagen

Presenter: Jim Lewis, SynthWorks Design Inc, USA

# Introduction to FPGA VHDL Verification – using the world-wide exploding UVVM

**Abstract:** There is a huge efficiency and quality potential in making good and well-structured testbenches. This applies to most developers and most companies. Improvement here is actually easy and does not require any investment at all. In fact – if you do this right – you will save a lot of time and improve quality already in your first project. The examples used are from the open source Universal VHDL Verification Methodology, but they show best practices for modern VHDL verification. UVVM has exploded over the last two years from 0 to 10% world-wide and increasing faster than ever. UVVM is recommended by Doulos for TB architecture, and we are cooperating with ESA to extend the functionality even further.

This presentation will show you the basics of making good testbenches, give you a fast introduction to UVVM Utility Library, BFMs and VVCs, - and show you step-by-step how to get started in only 4 minutes.

Event: Stockholm

**Presenter:** Espen Tallaksen, Bitvis and CGI, Norway

# Functional Safety for FPGAs

**Abstract:** Everybody is talking about and many companies are jumping on the functional safety train. The latest industry study from the Wilson Research Group shows, that almost 2/3 of today's European FPGA design projects are used within a safety application, i.e. autonomous driving or airplanes. Such safety applications require a high quality and a high reliability of the FPGAs. But the truth is, that more than 70% of these FPGA designs still have non-trivial bugs which escape to production. Functional Safety is driving down risk of Electrical and Electronics malfunctioning due to failures. Standards like ISO 26262 or IES 61508 focus on two areas of faults: Systematic Faults and Random Faults. In this presentation Stefan Bauer, one of Mentor's verification experts, will give an introduction to the ISO 26262 standard and how Mentor's overall functional safety flow can help to verify Systematic Faults and Random HW Faults.

Event: Stockholm, Copenhagen

Presenter: Stefan Bauer

Comapany website: https://www.mentor.com/

## FPGA-based security solutions for IoT and Industry 4.0

Abstract: This presentation discusses the benefits of FPGA-based security solutions and compares them to the softwarebased approach for addressing the challenges of Industry 4.0 and IoT. After a short introduction to cryptography, the main content of the presentation is an example of an FPGA-based communications endpoint implementation.

Event: Stockholm

Presenter: Matti Tommiska, Xiphera Oy, Finland Comapany website: <a href="http://www.xiphera.com">http://www.xiphera.com</a>

# Thank you Sponsors!